## Data Plane Processing Acceleration Framework

(Focusing on its Impacts to Internet Protocols)

draft-cao-dataplane-acceleration-framework-00

Zhen Cao China Mobile

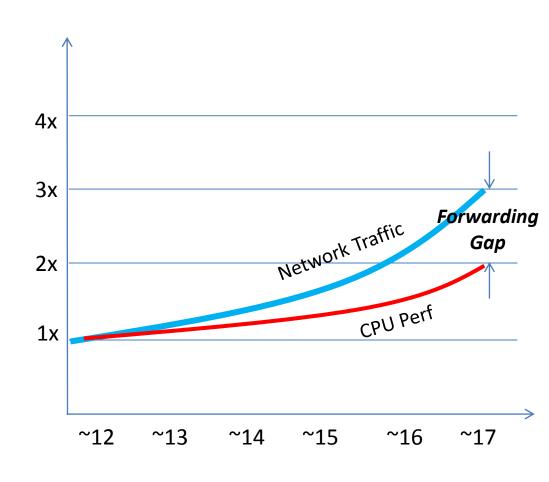

#### The Matter of Fact

- CAGR of Global Internet

Traffic is 24% \*

- Fixed CAGR = 21%

- Mobile CAGR = 68%

- Chipset performance CAGR is around 14%

- The 'Forwarding Gap' is therefore formed

<sup>\*</sup> Cisco Visual Networking Index: Forecast and Methodology, 2012–2017

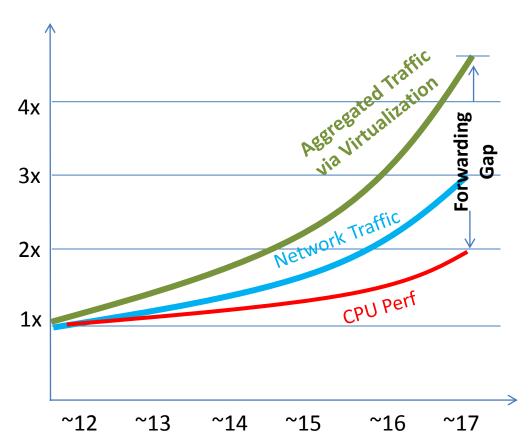

# The Matter of Fact, magnified by virtualization

- Virtualization technology increases traffic within appliances

- The 'Forwarding Gap' is therefore magnified

## Current practice to cover the 'Forwarding Gap'

- Data Plane Processing Acceleration

- Data Plane Develop Kit, i.e. DPDK

- Accelerated virtual switch

- Open Data Plane project (www.opendataplane.org)

- Tricks essentially it is to create 'Fast Paths'

- Efficient Run-time Memory Allocation, e.g., no malloc

- Minimize Data Copies in Memory

- Align data structures for best cache usage

- Have data at the right place at the right time

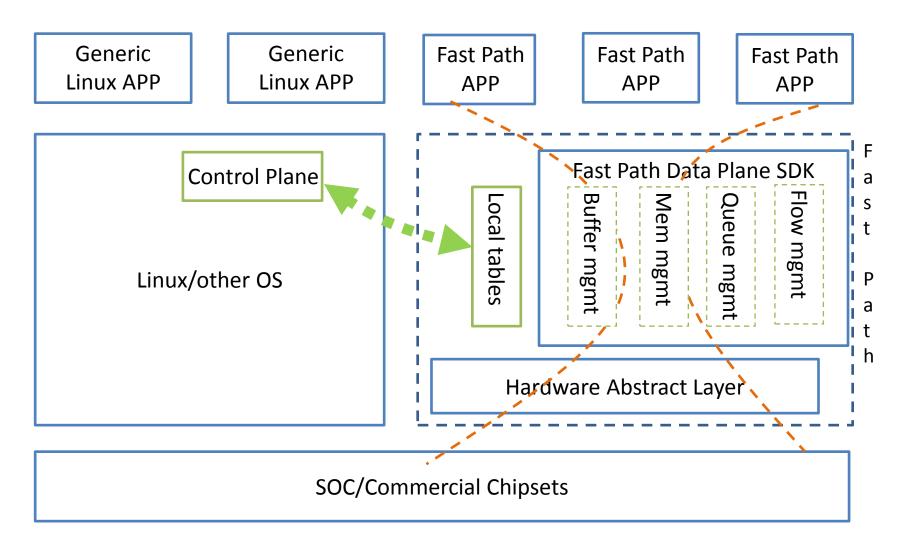

### Fast path within one device

HAL: Separating Data Plane Application Design from Implementation Design

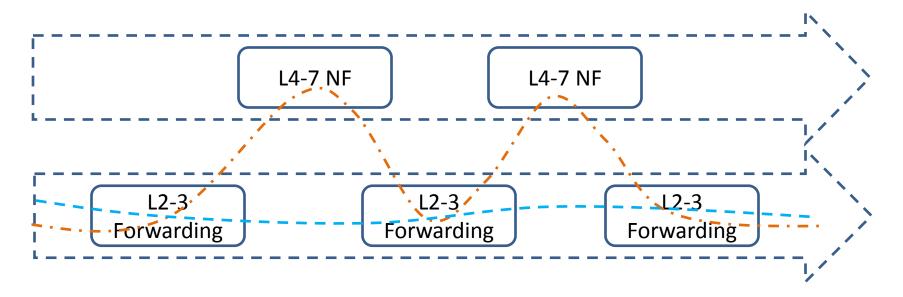

#### Fast Path across devices

- The higher layer the packet is being processed, the more challenge to its performance

- For some L4-7 network functions, the NF can establish the session and offload the traffic to the L2-3 infrastructure.

- Information (meta-data) conveyed from the NFs to bare metal forwarding devices

#### Relations to IETF STD

|                                                                                                 | Fast Path within one device | Fast path over multiple devices                                         |

|-------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------|

| Abstract APIs that abstract the buffer/memory/flow/q ueue management over multiple chipset arch | Doable but not abstract API | North-bound API,<br>depending on the<br>necessity of the below<br>entry |

| Communication between control and data plane                                                    | Wire-invisible (DMS)        | Wire-visible ••                                                         |

### Next Steps?

Comments welcome

Interested partners welcome